▶ Intel Details Core Ultra ‘Meteor Lake’ Architecture, Launches December 14

▶ Intel's Meteor Lake GPU Doubles Integrated Graphics Performance Per Watt

▶ Intel Announces 288-Core Processor, 5th-Gen Xeon Arrives December 14

▶ Intel Displays Arrow Lake Wafer With 20A Process Node, Chips Arrive in 2024

▶ Intel Flashes World’s First UCIe-Connected Chiplet-Based CPU

▶ Intel Shows Off Lunar Lake-Based PC, Unveils Panther Lake for 2025

Intel CEO Pat Gelsinger announced at the company’s Innovation 2023 conference that it has a new Sierra Forest Xeon processor with 288 E-cores coming to market in the future. Each core is single-threaded, so Intel’s new chip packs 288 physical cores and comes on the heels of Intel’s previously announced 144-core Sierra Forest processors. Intel also announced that its fifth-gen ‘Emerald Rapids’ Xeon will arrive on schedule on December 14.

The new Sierra Forest chips wield an E-core-based architecture that delivers the ultimate in threaded heft for scale-out, cloud-native, and containerized environments. You can read the deep dive architectural details here, but the big takeaway is that the chips employ CPU chiplets with the Intel 3 process combined with twin I/O chiplets based on the Intel 7 node to provide a flexible architecture that can scale to higher core counts with the addition of more chiplets.

The new 288-core model isn’t entirely surprising, as the company’s Granite Rapids architecture, which it also uses for Sierra Forest, can accommodate up to three compute chiplets packed with cores. Intel can pack 144 E-cores into a single chiplet.

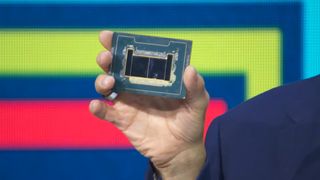

Intel recently slipped and accidentally revealed what is thought to be its 144-core Sierra Forest chip package in a press video that was later redacted. The large center die houses the CPU cores, while the two smaller die house I/O functions. We calculated that this single 588mm^2 I/O die can accommodate the originally-announced 144 E-cores in the center die, but Intel has Granite Rapids chips based on this same design that come with up to three compute chiplets.

As you can see in the above album, Granite Rapids and Sierra Forest share the same overall design, but the former comes with variants that can house one, two, or three CPU chiplets. Intel’s new 288-core behemoth simply employs two of the E-core-laden dies to reach its higher core counts. That means Intel could also release a model with three CPU chiplets, thus totaling 432 cores in a single massive chip. Of course, memory bandwidth, thermals, and TDP could be factors that prevent a three-chiplet monster, but only time will tell.

| Row 0 - Cell 0 | 2023 | 2024 | 2025 |

| Intel P-Cores | Emerald Rapids - Intel 7 | Sapphire Rapids HBM | Granite Rapids - Intel 3 | Row 1 - Cell 3 |

| AMD P-Cores | 5nm Genoa-X | Turin - Zen 5 | — |

| Intel E-Cores | — | 1H - Sierra Forest - Intel 3 -144 Cores | Clearwater Forest - Intel 18A |

| AMD E-Cores | 1H - Bergamo - 5nm - 128 Cores | — | — |

Here we can see how Intel’s roadmap looks next to AMD’s data center roadmap. AMD’s competing 128-core, 256-thread Bergamo takes a very similar core-heavy approach as Sierra Forest by leveraging AMD’s dense Zen 4c cores. Bergamo is already on the market, while Intel’s first Sierra Forrest chips won’t arrive until the first half of 2024. AMD hasn't outlined its second-gen Zen 4c model. Intel now has its second-gen E-core-powered Clearwater Forest on the roadmap for 2025.

Intel also announced that its fifth-gen ‘Emerald Rapids’ Xeon arrives on-schedule on December 14, which is a good sign as the company’s roadmap remains on track. Emerald Rapids will face off with AMD’s 5th-gen EPYC Turin chips that launch before the end of 2024.